Thermal interface materials for electronic devices

Abstract

Packaging electronic devices is a growing challenge as device performance and power levels escalate. As device feature sizes decrease, ensuring reliable operation becomes a challenge. Ensuring effective heat transfer from an integrated circuit and its heat spreader to a heat sink is a vital step in meeting this challenge.

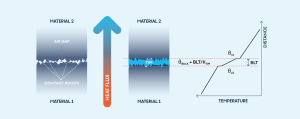

The projected power density and junction-to-ambient thermal resistance for high-performance chips at the 14 nm generation are >100 Wcm−2 and <0.2 °CW−1, respectively. The main bottleneck in reducing the net thermal resistance are the thermal resistances of the thermal interface material (TIM). This review evaluates the current state of the art of TIMs. Here, the theory of thermal surface interaction will be addressed and the practicalities of the measurement techniques and the reliability of TIMs will be discussed. Furthermore, the next generation of TIMs will be discussed in terms of potential thermal solutions in the realisation of Internet of Things.

Copyright © 2021 Nexalus Ltd. All rights reserved.

a. Tyndall National Institute, University College Cork, Cork, Ireland

b. Stokes Laboratories, University of Limerick, Limerick, Ireland

c. School of Physics, CRANN Nanotechnology Institute, Trinity College Dublin, Dublin 2, Ireland

d. Department of Mechanical & Manufacturing Engineering, Trinity College Dublin, Dublin 2, Ireland

e. CONNECT, Dunlop Oriel House, Trinity College, Dublin, Ireland

Kafil M. Razeeb, Eric Dalton, Graham Lawerence William Cross, Anthony James Robinson

Featured

Posts

Nexalus Selects Alps Alpine as Global Manufacturing Partner for Next Generation Thermal Management in Digital Infrastructure

Knowledge HubWhat Porsche’s shift from air to water cooling teaches us about thermal management in data centers

Knowledge Hub

Assessing Alps Alpine’s Valuation After The New Nexalus Liquid Cooling Partnership

Knowledge Hub

Is this the ‘Penicillin’ of keeping data centers cool?

Knowledge Hub

This university campus is heated by an AI data center. Your home could be next

Knowledge Hub

Time's 2025 list of Best Inventions

Knowledge Hub